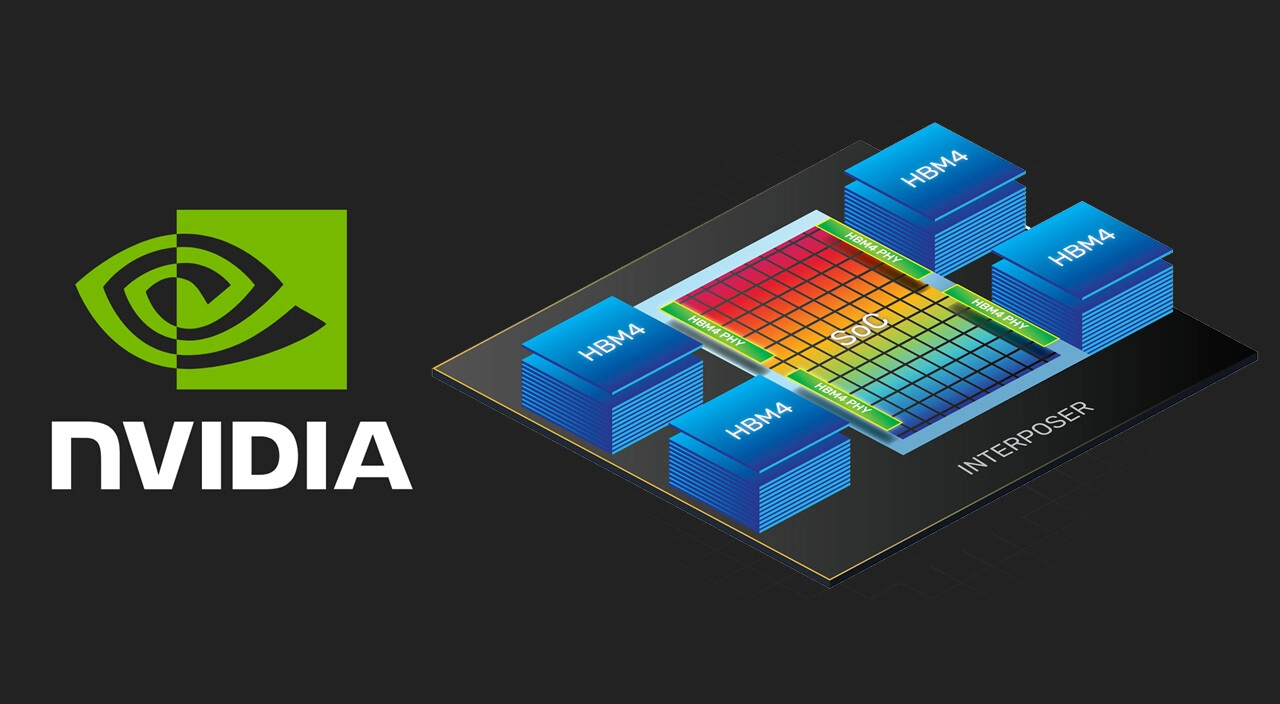

Theo các nguồn tin thị trường, NVIDIA đang có kế hoạch phát triển thiết kế Đế Bộ nhớ Băng thông Cao (HBM) của riêng mình, với mục tiêu sản xuất trên quy trình 3nm và việc sản xuất thử nghiệm dự kiến bắt đầu vào cuối năm 2027. TrendForce, trích dẫn từ Commercial Times, coi đây là một động thái chiến lược cho phép NVIDIA kiểm soát các thành phần logic cơ bản của các mô-đun HBM bất kể nhà sản xuất bộ nhớ nào cung cấp các lớp bộ nhớ xếp chồng.

Tin tức này đã làm đảo lộn ngành công nghiệp HBM, nơi SK Hynix hiện đang thống trị. Mặc dù SK Hynix chủ yếu sử dụng các giải pháp Đế Nội bộ, nhưng họ vẫn dựa vào các quy trình sản xuất tiên tiến từ các công ty như TSMC để đạt tốc độ trên 10 Gbps. Các nhà sản xuất bộ nhớ thường thiếu khả năng thiết kế phức tạp cần thiết cho việc phát triển Đế Nội và ASIC tinh vi.

Kế hoạch của NVIDIA dường như nhằm mục đích thắt chặt quyền kiểm soát hệ sinh thái của mình thông qua nền tảng NVLink Fusion, mang đến cho khách hàng nhiều lựa chọn kết hợp hơn. Tuy nhiên, các nhà cung cấp dịch vụ đám mây có thể phản đối các giải pháp Đế đế của NVIDIA, vì nhiều nhà cung cấp ban đầu đã chuyển sang phát triển ASIC để giảm sự phụ thuộc vào NVIDIA. Đồng thời, SK Hynix vẫn tiếp tục thúc đẩy công nghệ HBM4 của mình. Gần đây, công ty vừa xuất xưởng các mẫu 12 lớp với dung lượng 36 GB và tốc độ hơn 2 TB mỗi giây (nhanh hơn 60% so với HBM3E).

HBM4 dự kiến sẽ mang lại tốc độ cao hơn và khả năng xếp chồng với tích hợp đóng gói phức tạp hơn. Như chúng tôi đã đưa tin trước đây, NVIDIA và AMD sẽ triển khai bộ nhớ HBM4 tùy chỉnh trong các bộ tăng tốc AI sắp tới của họ. Kết hợp với kế hoạch sản xuất Đế đế HBM của riêng NVIDIA và tiến độ sản xuất HBM4 được đẩy nhanh của SK Hynix, thị trường HBM sắp bước vào một giai đoạn cạnh tranh và thay đổi mới.

theo: TechPowerUp