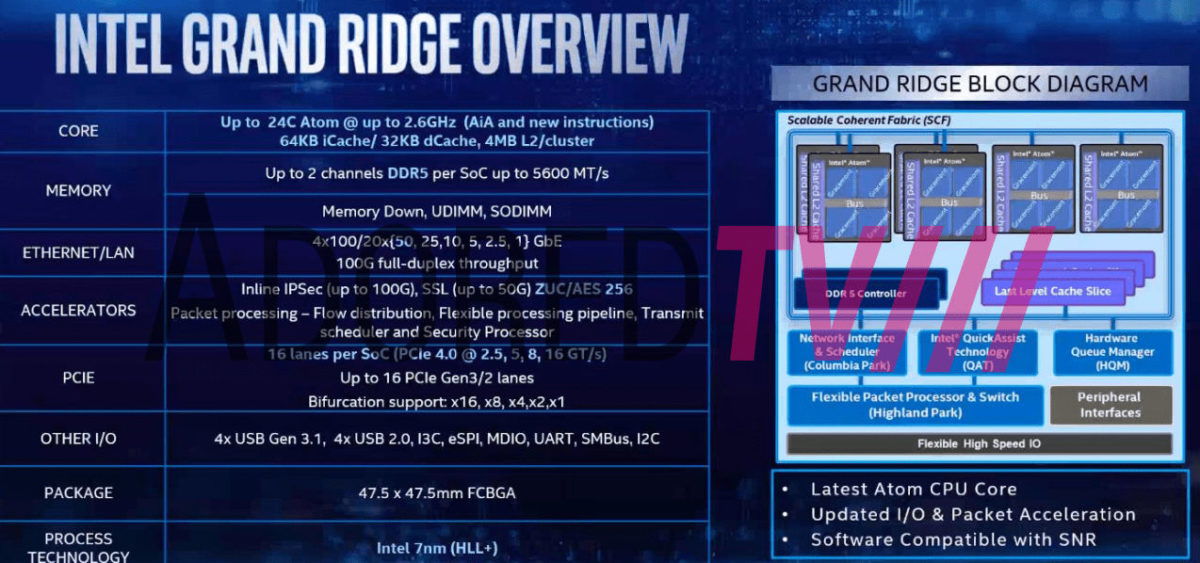

Một slide thuyết trình của nền tảng Grand Ridge sắp tới của Intel đã bị rò rỉ thông qua OverVolted của A doredTv. Với nền tảng Grand Ridge, Intel đang lên kế hoạch giới thiệu bộ xử lý dựa trên MCM với tối đa 24 nhân được liên kết bằng Scalable Coherent Fabric. Grand Ridge sẽ mở rộng danh mục đầu tư của Intel về phía Atom và sẽ có kiến trúc mới là Gracemont.

Kiến trúc Gracemont ban đầu được dự định sẽ được giới thiệu trong năm 2021 và tương đương với kiến trúc Golden Cove trên máy tính để bàn (thế hệ Willow Cove). Đây sẽ là bản cập nhật đầu tiên kể từ kiến trúc Tremont và sẽ là một bước nhảy vọt lớn về IPC và tính toán tổng thể (nhờ thiết kế MCM của nó) trong các phân khúc tiêu thụ năng lượng thấp. Nó cũng có tính năng hỗ trợ bộ nhớ DDR5, PCIe 4.0. Nó sẽ có thể có xung nhịp Boost lên đến 2.6GHz, khá nhanh cho một vi xử lý Atom và có thể hỗ trợ RAM tốc độ lên đến 5.0GHz.

Lõi xử lý sẽ có kích thước 47,5 x 47,5 mm và được chế tạo trên tiến trình 7nm HHL+ của Intel. VIệc chỉ định HHL+ rất thú vị và cho đến thời điểm hiện tại, chúng ta không chắc chắn về điều này. Raja Koduri của Intel đã sẳn sàng cung cấp các bản cập nhật quan trọng vào ngày 13 tháng 8 và chắc chắn rằng chúng ta sẽ có thêm thông tin chi tiết về mặt trận này sau đó.

Các loại bộ nhớ UDIMM và SODIMM đều được hỗ trợ và các chuyên ngành thích hợp như xử lý đóng gói, phân phối luồng, xử lý tuyến tính linh động, lập trình chuyền phát và bộ xử lý bảo mật cũng được tích hợp trên SoC. Nó dường như cũng có các tập lệnh mới với iCache 46KB, dCache 32KB và cụm L2 4MB. Nền tảng này có thể hỗ trợ 4x USB 3.1, 4x USB 2.0, I3C, eSPI, MDIO, UIART, SMBus và I2C.

nguồn: wccftech