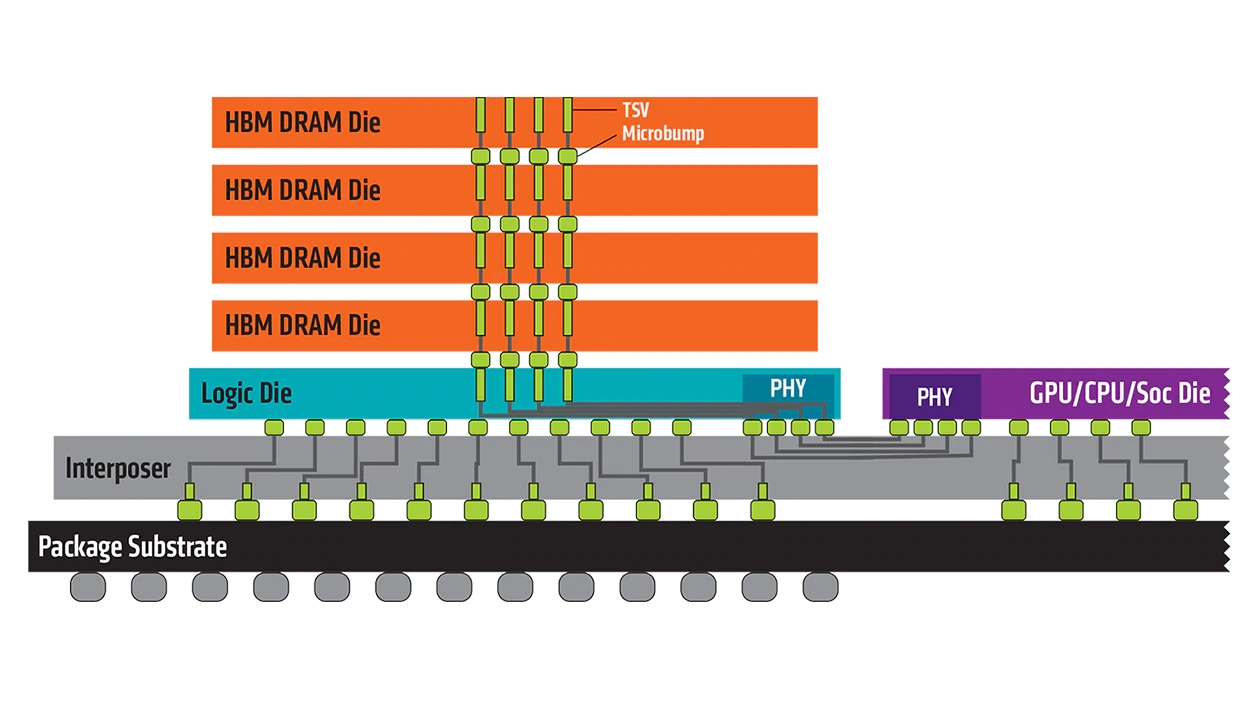

Các bộ gia tốc AI thế hệ tiếp theo của NVIDIA và AMD chắc chắn sẽ sử dụng bộ nhớ HBM4. Tuy nhiên, theo tin tức từ SemiAnalysis xác nhận, là các bộ gia tốc này sẽ lần đầu tiên sử dụng bộ nhớ HBM tùy chỉnh. Trong một ngăn xếp HBM, bao gồm các đế DRAM xếp chồng lên nhau lên đến 12 tầng, được kết nối với các TSV, có khả năng nhúng một đế tùy chọn với mạch logic/bộ gia tốc được tùy chỉnh theo nhu cầu cụ thể. Có vẻ như NVIDIA và AMD không chỉ đang khám phá tùy chọn này để tăng hiệu suất mà còn đang tích cực nghiên cứu một nền tảng tùy chỉnh, giúp các bộ gia tốc này vượt trội hơn một phần ba so với bất kỳ giải pháp ASIC nào của bên thứ ba. Vì mọi người đều đang cố gắng giành lấy một chút thị phần trong thế giới AI ASIC, NVIDIA và AMD phải đổi mới thiết kế của mình để luôn dẫn đầu.

“Chúng tôi kỳ vọng NVIDIA và AMD sẽ tung ra các triển khai HBM tùy chỉnh của họ với HBM4, trong khi các nhà thiết kế bộ tăng tốc khác có thể chỉ có triển khai đế chip tùy chỉnh bằng HBM4E vào khoảng thời gian năm 2027“, bài đăng của SemiAnalysis lưu ý. Điều này có nghĩa là trong khi các nhà thiết kế ASIC, chẳng hạn như Broadcom và MediaTek, sẽ có giải pháp hoạt động trong các chip năm 2027, thì NVIDIA và AMD sẽ có HBM4 tùy chỉnh hoạt động trong các sản phẩm từ năm 2026. Đối với NVIDIA, đây là kiến trúc “Rubin”, được cho là vượt trội hơn hẳn so với “Blackwell” hiện tại. Đối với AMD, đây là dòng bộ tăng tốc Instinct MI400, lần đầu tiên được ra mắt với quy mô rack-scale.

Các công ty thường lựa chọn bộ nhớ HBM có sẵn cho định giá mô hình tiêu chuẩn được triển khai bởi các nhà cung cấp như Samsung, Micron và SK Hynix. Tuy nhiên, khi đặt hàng số lượng lớn, như NVIDIA và AMD, họ có thể yêu cầu các tính năng hỗ trợ đặc biệt. Vì HBM có thể được sửa đổi đế chip, NVIDIA và AMD đã chuẩn bị các sửa đổi riêng của họ. Mặc dù đây có thể không nhất thiết là một khối tính toán mang lại sức mạnh TeraFLOPS, nhưng nó có thể sẽ là một khối xử lý dữ liệu/logic giúp định tuyến các gói dữ liệu hiệu quả hơn, giảm độ trễ và cải thiện hiệu suất. Đặc biệt là trong quá trình suy luận, khi độ trễ là yếu tố quan trọng nhất, việc có một HBM “thông minh hơn” có thể mang lại mức tăng đáng kể, lên đến hai chữ số, về thông lượng token.

theo: TechPowerUp