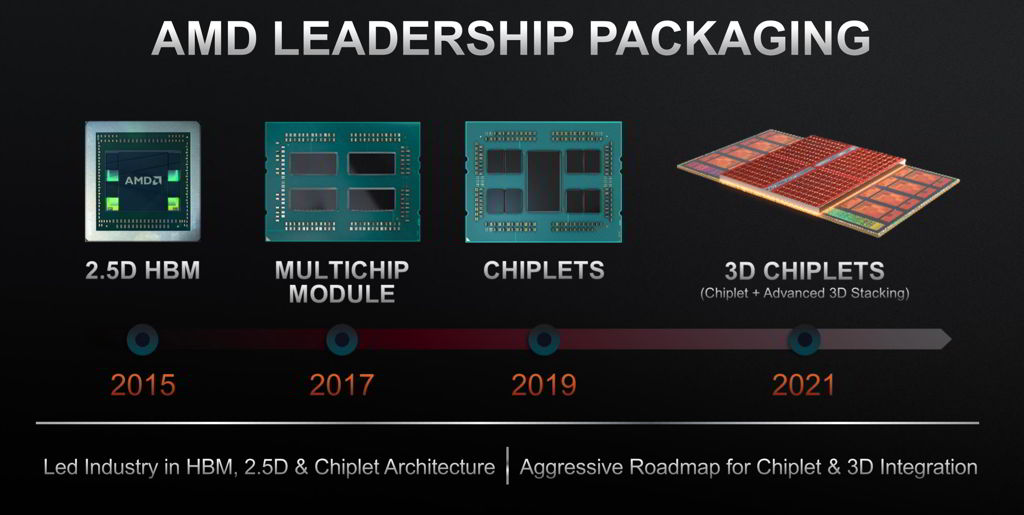

Vài tháng trước, AMD đã công bố thông tin về công nghệ mới cho CPU Ryzen của họ. Công nghệ 3D V-Cache của AMD có thể cung cấp đến 64MB cho bộ nhớ đệm L3 và xếp chồng lên trên các CPU Ryzen.

Dữ liệu từ các CPU AMD Zen 3 hiện tại cho thấy rằng thông quá thiết kế của AMD có khả năng cho phép bộ nhớ đệm 3D được xếp chồng lên nhau ngay từ đầu. Điều này chứng tỏ AMD đã phát triển công nghệ này trong nhiều năm qua.

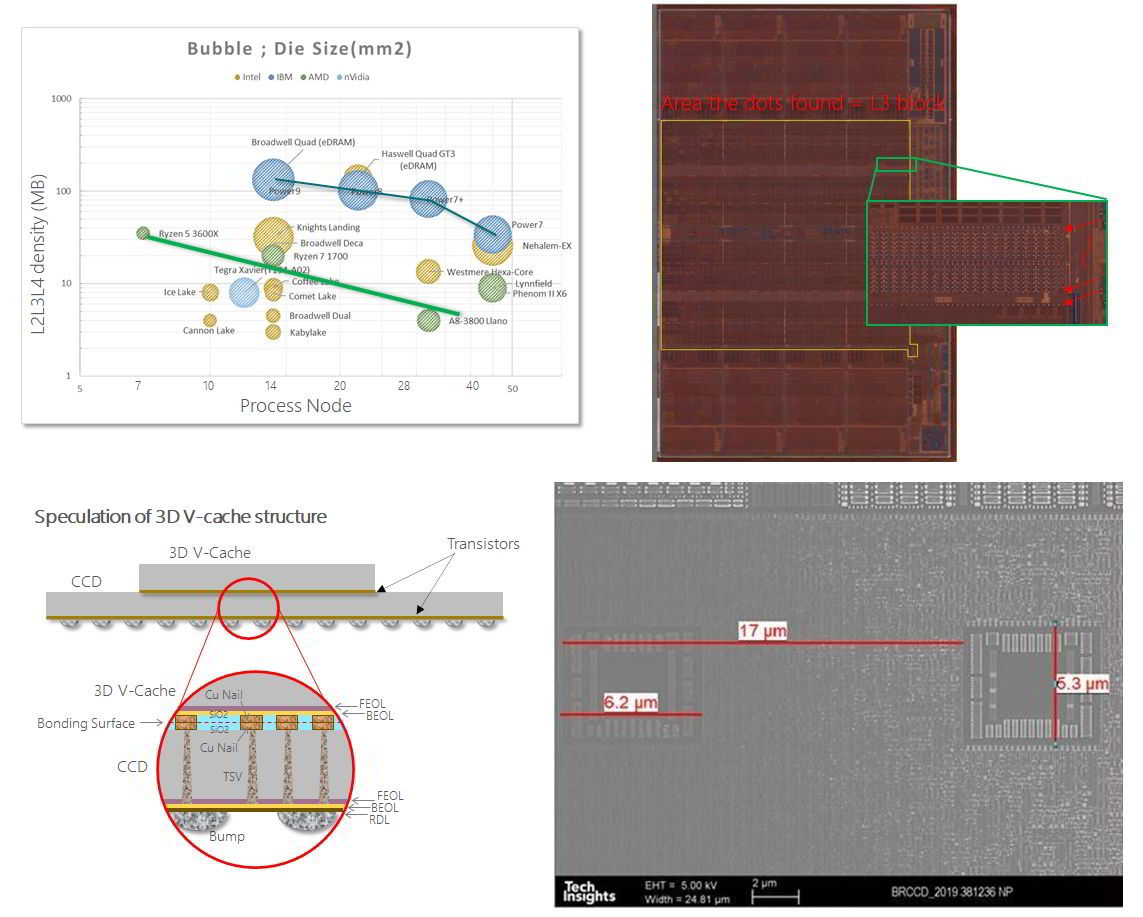

Và hiện tại, Yuko Fukuzaki đến từ TechInsights đã cung cấp thêm thông tin chi tiết hơn về tiến bộ mới này trong bộ nhớ đệm của AMD. Cung cấp cho chúng ta một cái nhìn sâu hơn, Fukuzaki đã tìm thấy các điểm kết nối cụ thể trên mẫu Ryzen 9 5950X. Cũng có một lưu ý về không gian bổ sung trên sản phẩm mẫu tạo khả năng truy xuất cho 3D V-cache bằng cách cung cấp nhiều điểm kết nối hơn.

Quá trình xếp chồng sử dụng một công nghệ được gọi là “xuyên qua silicon” hoặc TSV (through-silicon vias), tức là thêm vào một lớp SRAM thứ hai vào chip thông qua liên kết lai. Sử dụng đồng cho TVS thay vì hợp chất hàn thông thường cho phép tăng băng thông rộng hơn và hiệu quả hơn về nhiệt. Điều này thay cho việc sử dụng chất hàn để kết nối hai chip với nhau.

TechInsights đã nghiên cứu sâu hơn về cách 3D V-Cache kết nối và đã đưa ra những kết quả bao gồm thông tin TSV và không gian bên trong CPU cho các kết nối. Đây là kết quả:

- Độ lớn TSV: 17μm

- Kích thước KOZ: 6,2 x 5,3 μm

- TSV ước tính: khoảng 23 nghìn

- Vị trí TSV: giữa M10 – M11

Chúng ta chỉ có thể suy đoán về kế hoạch sử dụng 3D V-Cache của AMD với các cấu trúc trong tương lai, chẳng hạn như trong kiến trúc Zen 4 sẽ được phát hành trong tương lai gần. Và với những tiến bộ về công nghệ như thế này sẽ giúp cho AMD trở nên vượt trội hơn Intel khi mà chúng ta đã nhìn thấy tầm quan trọng của bộ nhớ đệm L3 bên cạnh số lượng nhân trong mỗi CPU.

nguồn: wccftech