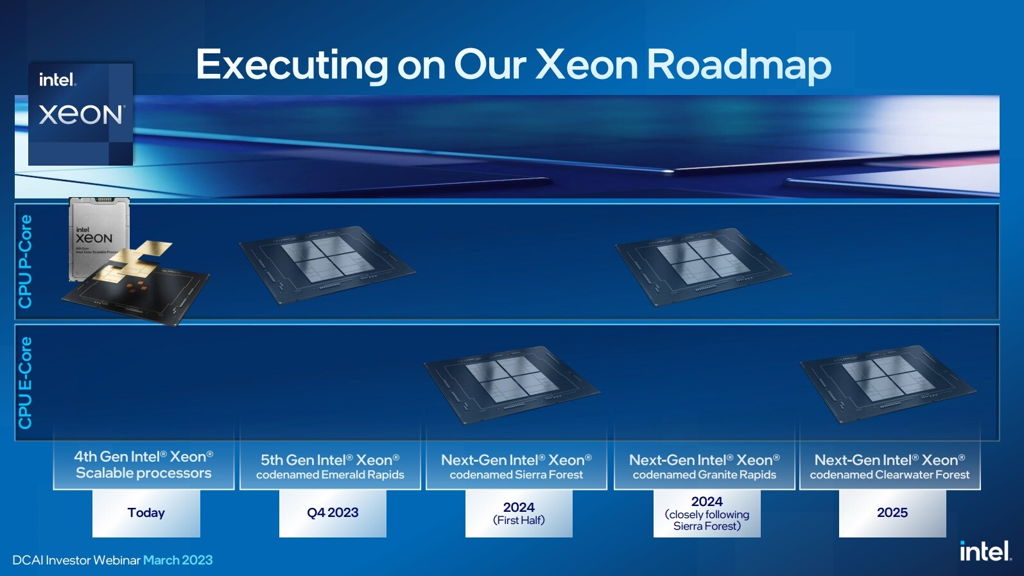

Intel gần đây đã chia sẽ kế hoạch của mình trong hai năm tới đối với dòng vi xử lý Xeon. Lộ trình CPU dòng Xeon mới đã được trình chiếu trong Hội thảo Data Center and AI Inves tor Webinar, cung cấp cho chúng ta các nhìn sơ lược về bốn kiến trúc sắp tới được lên kế hoạch phát hành vào năm 2025 gồ: Emerald Rapids, Sierra Forest, Granite Rapids và Clearwater Forest.

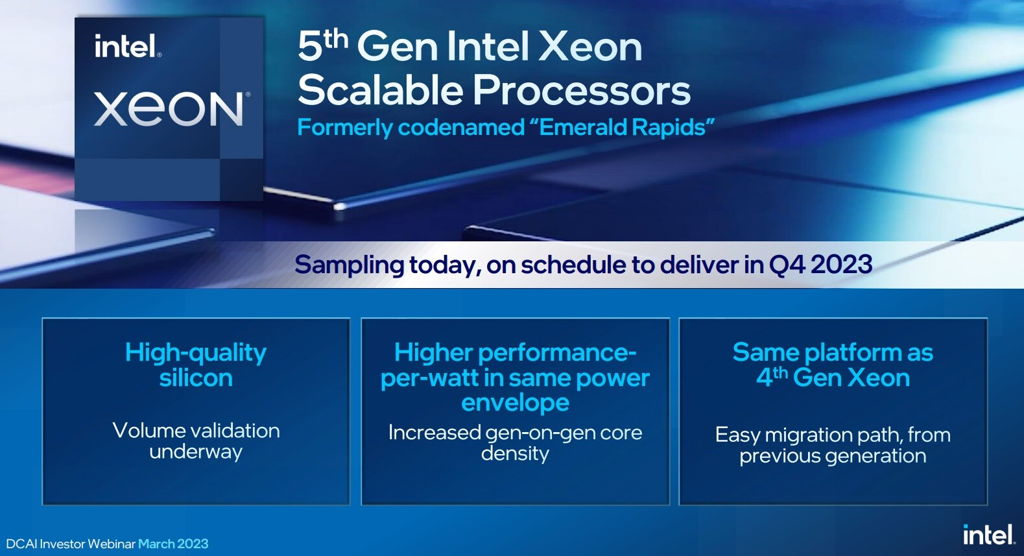

Sản phẩm đầu tiên xuất hiện sẽ là Emerald Rapids, bộ xử lý máy chủ P-Core tiếp theo của Intel. Là thế hệ thứ 5 của dòng Xeon có khả năng mở rộng, các mẫu thử kỹ thuật của CPU này đã được gửi đến khách hàng, việc phát hành sản phẩm dự kiến sẽ vào Q4 2023. Quá trình kiểm định số lượng lớn đang được tiếp tục và Sandra Rivera, Phó chủ tịch điều hành kiêm Tổng giám đốc Trung tâm dữ liệu và AI gần đây đã nói rằng chất lượng bóng bán dẫn của nhà máy là khá tốt.

Trong Q1 2024, Intel có kế hoạch ra mắt Sierra Forest, CPU máy chủ E-Core đầu tiên. Sierra Forest sẽ có 144 lõi trên mỗi socket và sẽ là kiến trúc đầu tiên dựa trên quy trình Intel 3. Sierra Forest đã đi vào hoạt động vào đầu quý này, những mẫu thử đầu tiên đã đến tay khách hàng.

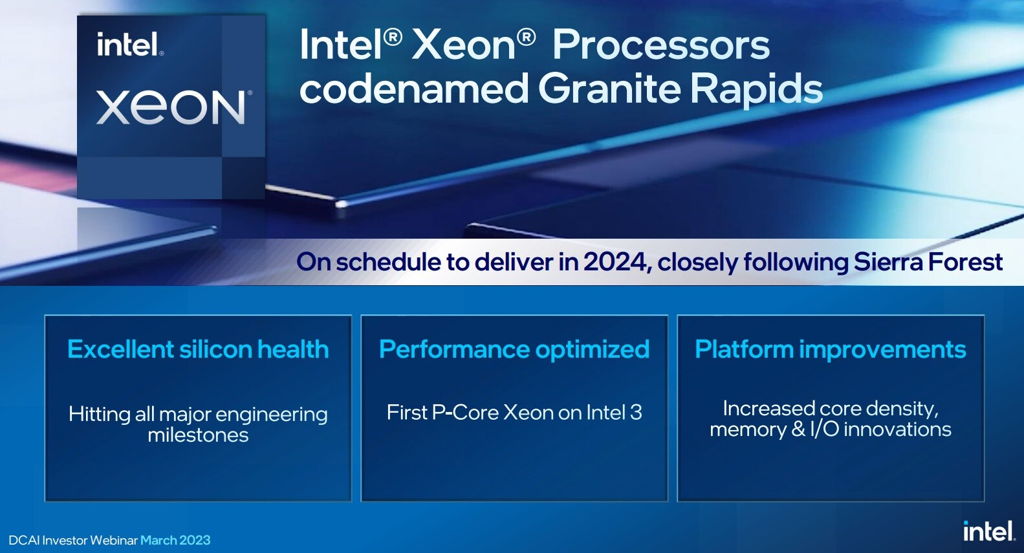

Granite Rapids sẽ theo sát Sierra Forest trong năm 2024, được đóng gói chỉ gồm các P-Cores. Mặc dù không có ngày ra mắt chính xác nhưng một số chi tiết đã được tiết lộ. Các chip mới sẽ chia sẽ nền tảng của chúng với các CPU Sierra Forest, giúp giảm thời gian phát triển và thiết kế. Granite Rapids đang vượt qua tất cả các cột mốc quan trọng, vì đã có những con chip thực tế được phân phối cho một số đối tác của Intel.

Ngoài ra, Spelman nói rằng Intel đang “xây dựng giao diện bộ nhớ nhanh nhất trên thế giới cho Granite Rapids”. Bộ nhớ mới này là một dạng DIMM mới có tên là Multiplexer Combined Rand (MCR). Intel khẳng định các mô-đun mới này có thể đạt tốc độ 8.800MHz, nhanh hơn đáng kể so với cac mô-đun bộ nhớ DDR5 cao cấp hiện nay.

Để kết thúc, Intel cũng tiết lộ Clearwater Forest. Giống như Sierra Forest, các CPU này sẽ chỉ đóng gói các lõi E-Core được xây dựng trên Intel 18A, quy trình mà Intel dự kiến sẽ thiết lập lại khả năng dẫn đầu quy trình đóng gói. Những con chip đầu tiên dựa trên kiến trúc này sẽ ra mắt vào năm 2025.

theo: KitGuru!