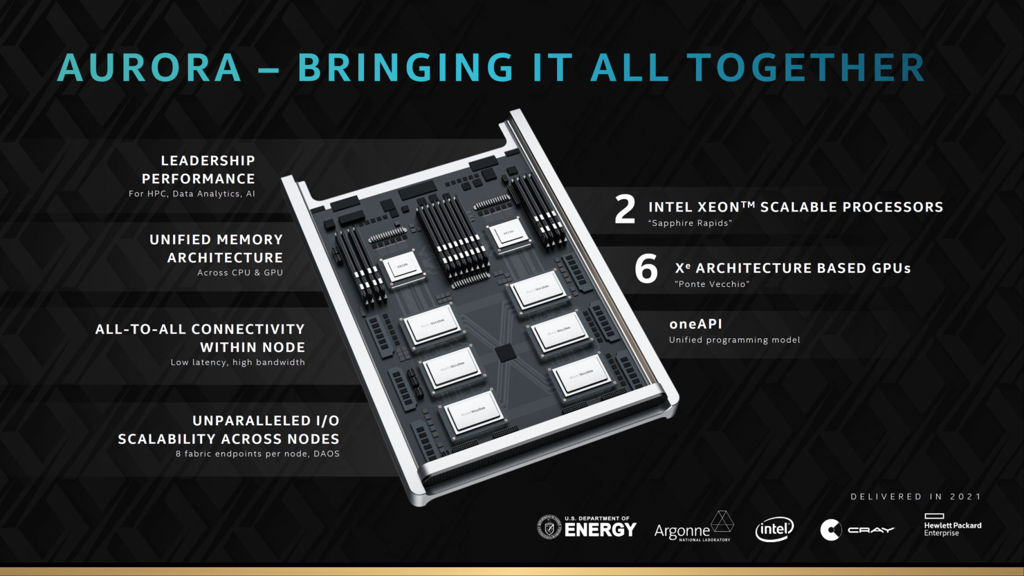

Siêu máy tính Aurora do Intel cung cấp sẽ chứa GPU Xe HPC “Ponte Vecchio” thế hệ tiếp theo và CPU Xeon Sapphure Rapids cũng đã được trình bày chi tiết hơn. Sẽ được ra mắt vào năm tới, siêu máy tính Aurora sẽ được triển khai tại phòng thí nghiệp quốc gia Argonne National Laboratory và sẽ là một trong những cỗ máy exascale đầu tiên trên Trái Đất.

Với dòng máy tính hiệu suất cao của Intel cho năm 2021, siêu máy tính Aurora vừa nhanh vừa thực sự ấn tượng ở góc độ kỹ thuật. Trong hội nghị thường niên ECP, những thông tin chi tiết về siêu máy tính này đã được tiết lộ, bao gồm cấu hình và thông số kỹ thuật phần cứng.

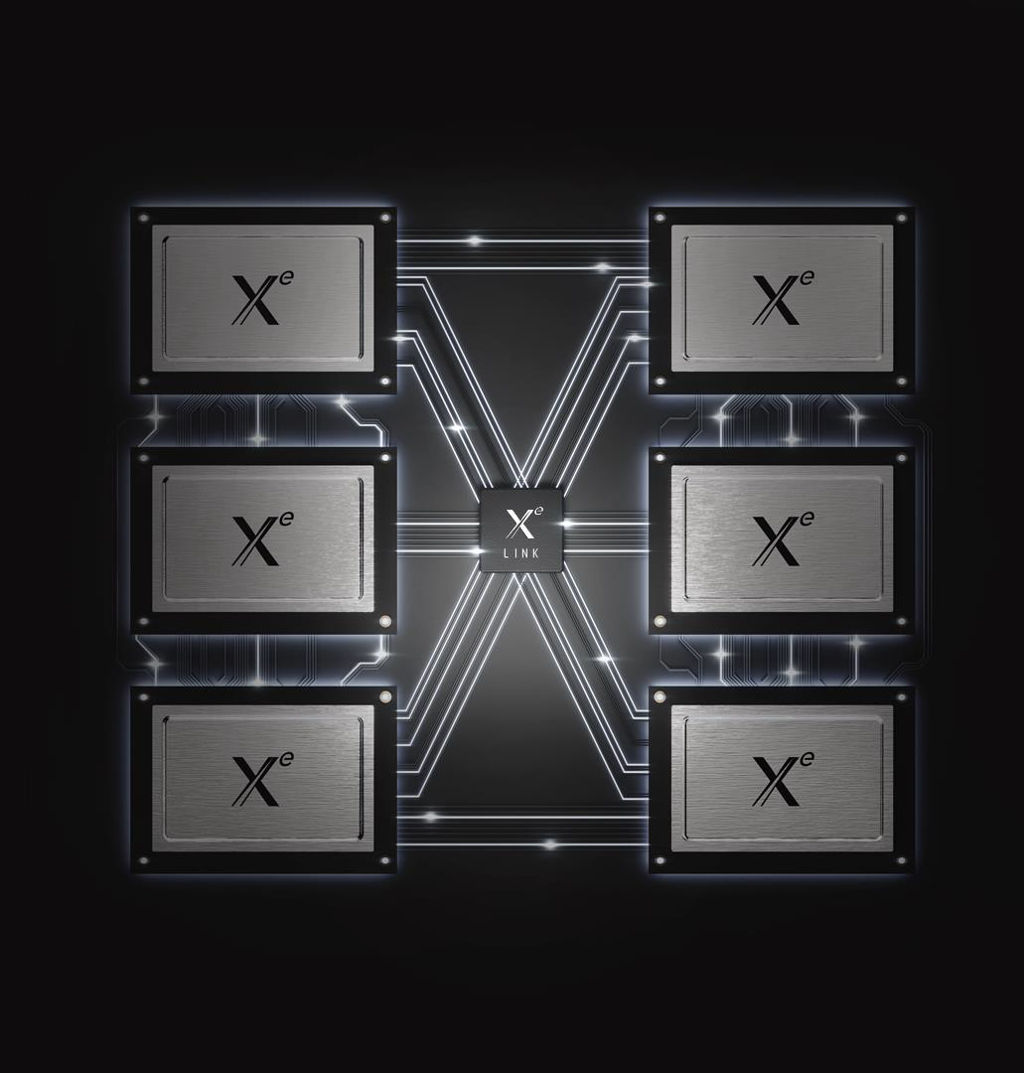

Siêu máy tính Aurora được lên kế hoạch triển khai tại Argonne vào năm 2021 và sẽ đạt đỉnh trên 1Exaflops về hiệu suất duy trì. Siêu máy tính này cũng sẽ được trang bị GPU Xe HPC ‘Ponte Vecchio’ 7nm của Intel và vi xử lý xeon Sapphire Rapids (10nm++) của Intel. Mỗi node sẽ bao gồm 6 GPU Xe HPC và 2 CPU Xeon Sapphire Radids. 5 GPU Xe HPC sẽ có kết nối toàn diện với băng thông tốc độ cao nhưng có độ trễ thấp. Một kiến trúc bộ nhớ hợp nhất sẽ có sẳn trên các CPU và GPU này.

Về bộ nhớ, lưu trữ và băng thông, chúng ta đang nhìn thấy hơn 10PB (Petabytes) bộ nhớ hệ thống và kết nối Crab Slingshot Fabric (nền tảng Shasta). Sẽ có tổng cộng 8 điểm Slingshot Farbic trên mỗi node trong một siêu máy tính Aurora. Siêu máy tính sẽ có hai hệ thống tập tin đa dạng với một trong số đó là DAOs (Distributed Asynchronous Object Store) hệ thống còn lại là Lustre. Dung lượng và băng thông chi tiết của từng hệ thống tập tin như được thể hiện bên dưới:

DAOs:

- Khoảng 230 PB dung lượng lưu trữ

- Băng thông lớn hơn 25TB/s

Lustre:

- Dung lượng lưu trữ hoàn chỉnh là 150 PB

- Băng thông khoảng 1TB/s

Một rack Aurora đơn sẽ được thiết kế bởi Cray như là một phần của nền tảng Shasta của họ, hỗ trợ nhiều loại CPU khác nhau và có các tủ rack được tối ưu hóa theo quy mô và mật độ, theo khả năng làm mát và băng thông mạng tốc độ cao. Cray cũng cung cấp các ngăn xếp SW của riêng mình để cải thiện tính mô-đun trong khi vẫn cung cấp một kết nối thống nhất và hiệu suất cao. Bản thân Slingshot là một loại siêu liên kết hế hệ thứ 8. Nó sử dụng các bộ chuyển mạch tốc độ cao do Rosetta cung cấp có băng thông lên đến 25,6Tb/s cho mỗi mạch (25GB/s mỗi hướng)

GPU Intel Xe HPC ‘Ponte Vecchio”

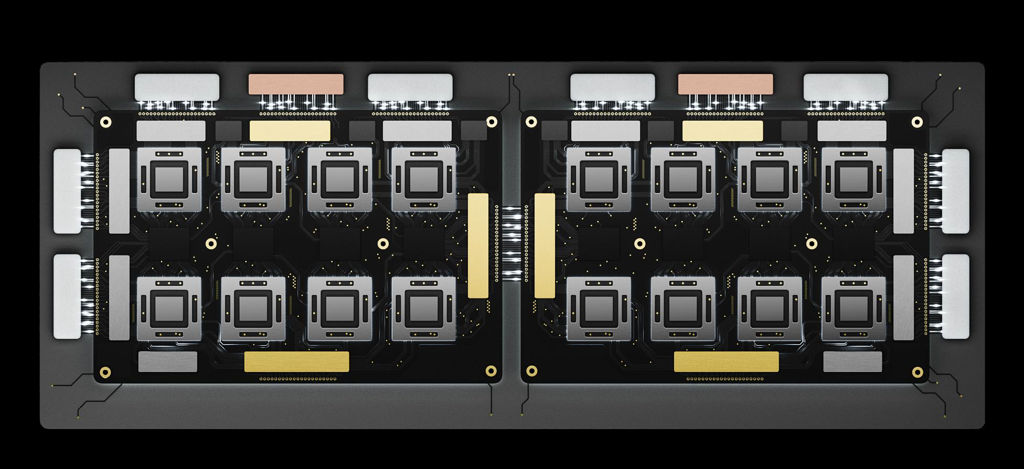

Đối với GPU Xe HPC ‘Ponte Vecchio” sẽ là sản phẩm 7nm dẫn đầu trong năm 2021. Nó sẽ có thiết kế đóng gói MCM dựa trên công nghệ đóng gói 3D Foveros. Mỗi GPU MCM sẽ được kết nối với các gói bộ nhớ HBM mật độ cao thông qua EMIB ngoài ra còn có Rambo Cache tốc độ cao. Cuối cùng, trong khi Slingshot cung cấp kết nối giữa các node, nhiệm vụ kết nối 6 GPU Xe HPC với nhau sẽ được đảm trách bởi Xe Link.

Trước đây Intel đã nói chi tiết rằng GPU Xe HPC của họ sẽ có 1000EU (Execution unit). Cho đến nay, chúng ta mới chỉ thấy Xe LP với 96EU và 768 nhân. Hiện tại, Intel có 8 EU mỗi cấp (subline). Một phần phụ trong GPU Gen12 tương tự như đơn vị SM của GPU NVIDIA hoặc AMD CU trong Shader Engine. Intel hiện có 8 EU mỗi cấp cho GPU Gen9.5 và Gen11 của họ, vì vậy nếu giữ nguyên cấu trúc phân cấp đó, chúng ta có thể thấy một số lượng đáng kể các Superslide bao gồm nhiều nhát. Mỗi EU Gen9.5 và Gen11 cũng chứa 8ALU và sẽ được giữ nguyên trên Gen12.

Làm tròn nó, một con chip 1000 EU sẽ chiếm tới 8000 nhân nhưng đã được xác nhận rằng 1000 chỉ là giá trị cơ bản và số lượng nhân thực tế lớn hơn rất nhiều. GPU Xe HP cấp độ 4 có 2048EU hoặc 16.384 nhân đã được chi tiết hóa nên có khả năng các bộ phận HPC sẽ lớn hơn thế nhiều. DƯới đây là số lượng thực tế của EU trên các GPU Xe HP dựa trên đóng gói MCM khác nhau của Intel cùng với số lượng nhân và TFLOP ước tính:

GPU Intel Xe HP (12.5) 1-tile: 512 EUs (dự đoán khoảng 4096 nhân, 12,2TFLOP giả định ở 1.5GHz và 150W)

GPU Intel Xe HP (12.5) 2-tile: 1024 EUs (dự đoán khoảng 8192 nhân, 20,48 TFLOP giả định ở 1.25GHz và 300W)

GPU Intel Xe HP (12.5) 4-tile: 2048 EUs (dự đoán khoảng 16.384 nhân, 36 TFLOP giả định ở 1.1GHz, 400W/500W)

Các lớp GPU Xe của Intel sẽ có chiều rộng vector thay đổi như được đề cập dưới đây:

SIMT (kiểu GPU)

SIMD (kiểu CPU)

SIMT + SIMD (hiệu suât tối đa

Raja đặc biệt nhấn mạnh về lớp GPU Xe HPC vì đó là những gì đáng để nói tại hội nghị dành cho nhà phát triển. GPU Xe HPC của Intel có thể mở rộng tới 1000 EUs và mỗi EU đã được nâng cấp để cung cấp sức mạnh tính toán double-precision floating-point tốt hơn 10 lần.

Các EU sẽ được kết nối với một loại bộ nhớ scalable memory fabric mới được gọi là XEMF (dạng ngắn của XE Memory Fabric) với một số kênh bộ nhớ tốc độ cao. Kiến trúc Xe HPC cũng sẽ bao gồm một bộ điệm thống nhất lớn được gọi là bộ đệm Rambo Cache sẽ kết nối nhiều GPU với nhau. Bộ đệm Rambo Cache này sẽ cung cấp một tính toán FB64 đỉnh cao bền vững trong suốt khối lượng công việc có độ chính xác đôi bằng cách cung cấp băng thông bộ nhớ lớn hơn. Về mặt tối ưu hóa quy trình, sau đâu là một vài cải tiến quan trọng mà Intel đã công bố cho node quy trình 7nm của họ so với 10nm:

Tỷ lệ mật độ cao gấp 2 lần so với 10nm

Đã được lập định tối ưu hóa node

Giảm 4 lần quy tắc thiết kế

EUV

Đóng gói Foveros và EMIB thế hệ tiếp theo

Các GPU Xe HPC sẽ sử dụng công nghệ Forveros để kết nối với bộ đệm Rambo Cache sẽ được chia sẻ trên một số GPU Xe HPC khác trên cùng một mạch chuyển đổi. Giống như các bộ xử lý Xeon, GPU Xe HPC của Intel sẽ đi kèm với bộ nhớ/bộ đệm tự sửa lỗi ECC và RAS cấp độ Xeon.

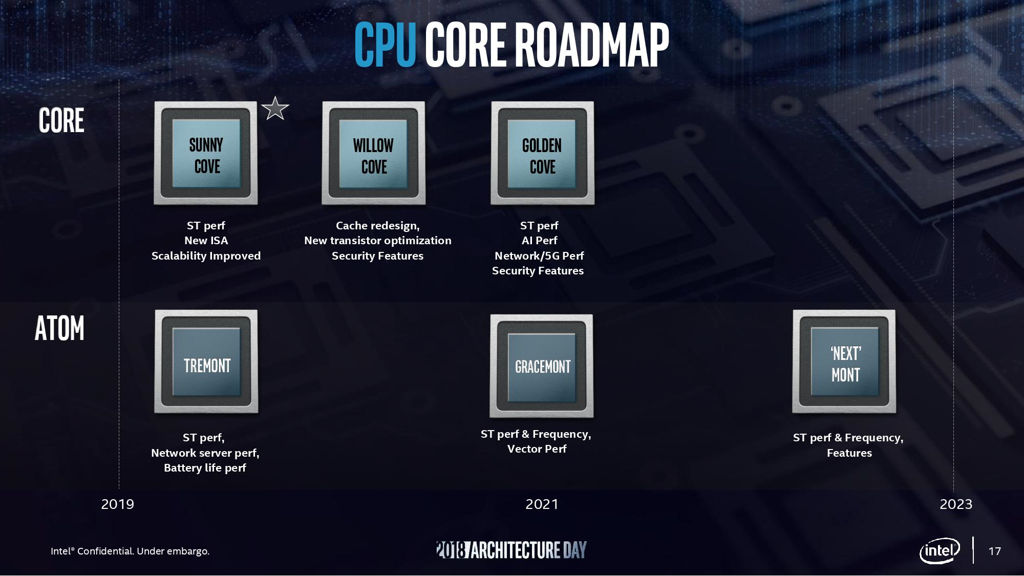

Vi xử lý Intel Xeon Sapphire Rapids 10nm++

Vi xử lý Sapphire Rapids 10nm++ dự kiến sẽ sử dụng kiến trúc lõi Willow Cove cập nhật thay thế cho Sunny Cove trong năm 2020. Dòng Sapphire Rapids sẽ sử dụng bộ nhớ DDR5 8 kênh và hỗ trợ PCIe Gen 5.0 trên nền tảng Eagle Stream. Nền tảng Eagle Stream cũng sẽ ra mắt socket LGA 4677 thay thế socket LGA 4189 trên nền tảng Whitley sắp tới của Intel dành cho loạt vi xử lý Cooper Lake-SP và Ice Lake-SP.

Điều này sẽ cho phép Intel kết hợp hoặc thậm chí vượt xa các dịch vụ EPYC của AMD nếu Milan kết thúc việc tái sử dụng DDR4 và PCIe Gen4 trên nền tảng EPYC Rome sắp tới. Gia đình Sapphire Rapids của Intel sẽ ra mắt cùng năm mà Intel ra mắt GPU Xe hiệu suất cao cho trung tâm dữ liệu của họ dựa trên quy trình 7nm.

Nền tảng này sẽ cạnh tranh với dòng EPYC Genova dựa trên kiến trúc Zen 4 của AMD, cũng sẽ chuyển sang một nền tảng mới hơn được gọi là SP5. AMD sẽ sử dụng bộ nhớ mới cùng với những tính năng mới cho dòng sản phẩm Genova bao gồm DDR5, PCIe Gen5,… Chúng ta không biết dòng sản phẩm mới này sẽ bao gồm những tính năng nào nhưng Intel cũng làm tương tự với việc hỗ trợ DDR5 8 kênh và kết nối mới cho nền tảng Eagle Stream.

nguồn: wccftech